无增益折衷的CMOS LNA输入匹配网络

如今,大多数无线接收器通常都需要有高增益的LNA。

作为接收器链中的第一个有源组件(active block),LNA应该提供足够的增益,以克服后续级带来的噪声,并尽可能减少噪声。

然而,在一些如IEEE 802.15.4的无线标准中,LNA的噪声系数(NF)不是一个关键的性能参数1,2。

NF要求可以适当放宽,以优化其他设计参数,如增益、功耗和芯片面积。

在这篇文章中提出的LNA是专门为IEEE 802.15.4标准设计的。

流行的LNA拓扑结构是源极电感负反馈(inductive source-degeneration)共源LNA(LCSLNA)、共栅LNA(CGLNA)和电阻反馈LNA(RFLNA)。

由于其方便的输入匹配、高增益和低噪声,L-CSLNA通常是超低功耗窄带应用的首选3-6。

但是,其增益性能会受到输入匹配条件的限制。

在L-CSLNA的高增益和良好的输入匹配之间存在一个折衷问题。

在这篇文章中,提出的LNA的输入匹配是通过一个电容反馈方案和一个Л匹配网络实现的。

相比L-CSLNA,电容反馈有助于减少输入匹配所需的电感数目。

此外,利用Л匹配网络可实现较高的增益和更大的设计自由度。

Chung和Shahroury实现了利用电容反馈进行输入匹配的概念7。

不过,所使用的LNA采用的是非级联结构。

为了实现高反向隔离,它利用了一个多级结构,这导致了非常高的功耗。

提出的LNA采用单级级联结构,给出了输入匹配、增益和NF的详细分析。

LNA是采用IBM 0.13μm RF CMOS技术实现的。

源极电感负反馈共源LNA

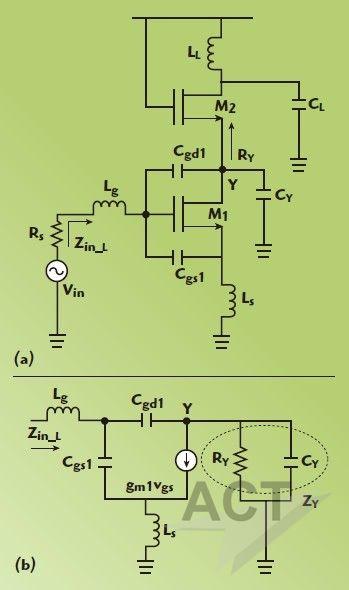

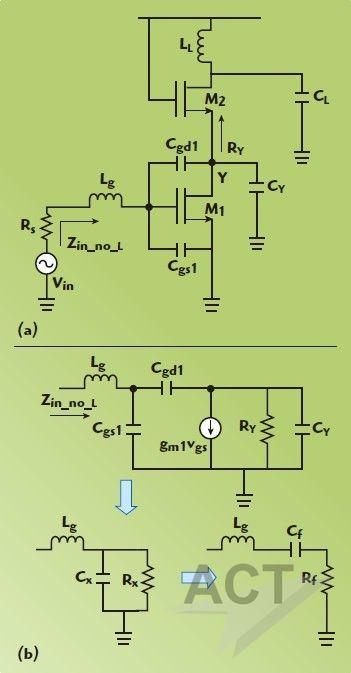

输入阻抗分析的L-CSLNA原理图及其等效小信号电路如图1所示。

CY包括节点Y的所有寄生电容,可以近似为:

![]()

RY是来自节点Y的M2源的总阻抗,在此电路中,RY可近似为1/gm2,此处的gm2是晶体管M2的跨导。

推导出的L-CSLNA的输入阻抗是:

其中是工作频率,Cgs1和Cgd1是寄生栅源和栅漏电容,gm1是晶体管M1的跨导。

当 ![]() 时,Zin_L可以简化为:

时,Zin_L可以简化为:

![]()

这与经典结果是一致的。

在谐振频率,输入阻抗Rin_L等于gm1Ls/Cgs1和晶体管gm1的跨导,可有效地提高Geff_Lgm1,其中Geff_L是:

0是谐振频率。

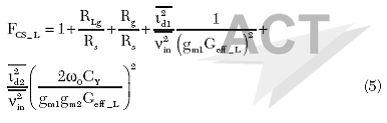

在输入匹配条件下这个LNA的噪声系数是:

在方程5中,RLg是电感Lg的寄生串联电阻,Rg是晶体管M1的栅极电阻, 和 分别是晶体管M1和M2的漏电流噪声, 是输入源电压噪声。

大gm1和小Cgs1是实现高增益和低噪声所必需的4,5。

由于输入匹配条件,Ls的值通常相当小。

小Ls的要求有时会成为LNA设计的一个困扰,因为不是所有的电感值都适用于工艺设计套件(PDK)。

提出的具有匹配网络的电容反馈CSLNA

Cheng7介绍的LNA使用了输入器件的寄生栅漏电容和输出电容CL,以形成电容反馈匹配网络。

只有一个电感用来实现输入匹配。

不过,该分析只适用于非级联结构。

对于CS拓扑结构,要有高反向隔离和良好的稳定性,级联是首选的结构。

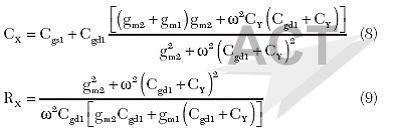

在这里,介绍了级联结构的分析。

其原理如图2所示。

基于小信号电路(b),级联电容反馈LNA的输入网络可以转换为一个包括Lg、Cf和Rf的串联RLC匹配网络。

Cf和Rf的值可以推导得出:

![]()

且

![]()

Cx和Rx可以按以下方程计算

为了实现输入匹配,Rf的设计等于Rs。

此输入匹配网络的有效增益是:

该LNA在输入条件观看到的噪声系数可以推导得出:

与L-CSLNA相比,电容反馈LNA需要的输入匹配电感数量较少。

但这样做的好处伴随着较高NF的折衷问题,这可以从方程5和11观察到。

从方程4和10看到,以上讨论的两个LNA的输入网络的有效增益受到了50 Ω匹配条件的限制。

为了实现良好的输入匹配,Rf和(gm1Ls/Cgs1)必须匹配到50 Ω。

这将限制Geff_L和Geff_no_L的选择,因此限制了这两个LNA可实现的增益。

在这两个LNA中存在着高增益和良好的输入匹配之间折衷的问题。

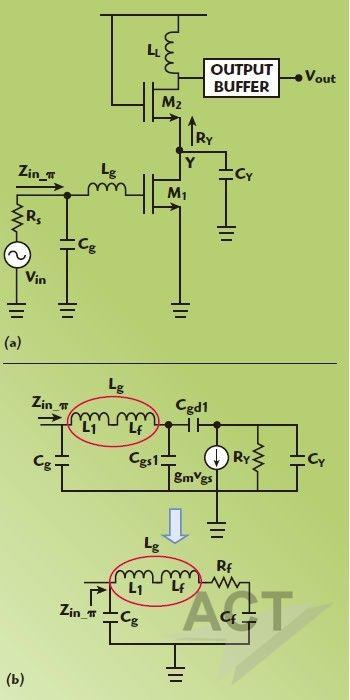

提出的LNA增加了一个并联电容器Cg,如图3所示前述的栅极电感创建了一个Л匹配网络。

它显示了用于提出的LNA(b)的输入阻抗计算的小信号电路。

如上所述,Rf和Cf是由电容反馈机制形成的。

电感Lg可分为两个较小的部分:L1和Lf。

这两个电感与Cg和Cf谐振。

共振频率的输入阻抗为:

![]()

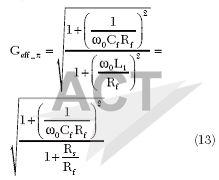

提出的输入匹配网络的有效增益是:

方程13显示,提出的LNA的有效增益可以通过减小Rf值来增加,而不像电容反馈LNA和L-CSLNA,其有效增益受到50 Ω匹配条件的限制。

当减小Rf时,根据方程12,LNA的输入阻抗可以通过减小L1匹配到50 Ω。

电容Cg和电感L1为LNA设计增加了额外的自由度。

有效增益不再受到输入匹配条件的限制。

因此,提出的LNA将能够实现比L-CSLNA和电容反馈LNA高得多的增益。

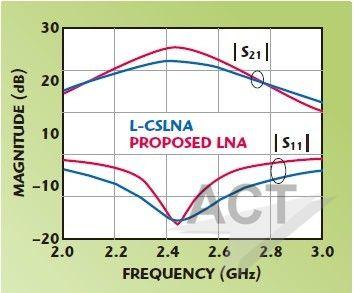

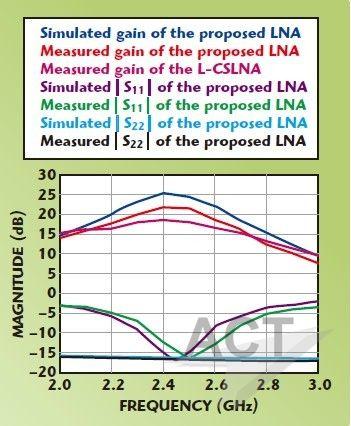

图4显 示了在同样功耗水平和输出负载条件下,提出的LNA和L-CSLNA的S21和S11的响应情况。

在要测试的频率下,两个LNA的设计具有相同的输入匹 配。

提出的LNA显示了更好的增益性能。

LNA的增益为3 dB,高于L-CSLNA。

带宽(BW)随着匹配网络的有效增益而增加。

但是,如下所示,这个仿真中的LNA的带宽对所需标准来说仍然足够大。

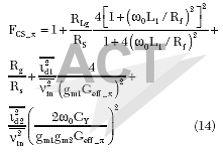

提出的 LNA的噪声系数是:

方程11相比,由于Л网络的缘故,RLg的噪声贡献增加了。

不过,当LNA设计的Geff_高于Geff_no_L时,来自 的噪声贡献可以减少。

因此,它可以弥补由RLg造成的损耗。

此外,当Geff_增加时,级联级的噪声贡献也会减少。

对于频率f0条件下的窄带LNA,设计步骤总结如下。

为实现最好的晶体管性能,要采用最小的通道长度。

为了实现高增益和低噪声,Rf的值要设计得尽可能小。

不过,正如上面所讨论的,所需应用的带宽必须保持足够。

此外,当Rf下降时,所需的L1减小,但所需的Cg增加。

由于Cg的负极板直接连接到地,其值应该不会太大。

Cg和L1的值来自于方程12。

根据所需的增益和可用芯片面积确定Lf的值。

Lf越大,得到的增益越高。

在f0,Cf与Lf谐振。

鉴于特定漏电流和所需的Rf和Cf值,可根据方程6-9设计晶体管的尺寸和偏置。

为了验证这一理论,采用IBM的0.13 μm RF CMOS技术设计和制作了一个LNA。

其原理如图3(a)所示。

所有电感器均在片上。

在要测试频率,电感LL将与晶体管M2的漏极节点的总电容产生谐振。

电感Lg和电容Cg的设计可以满足匹配条件。

该LNA的第二级是输出缓冲区。

输出缓冲区的目的是要将输出端口匹配在测设备的50 负载。

缓冲区的负载效应与LNA级的混频器加载效果大致相同。

测量结果

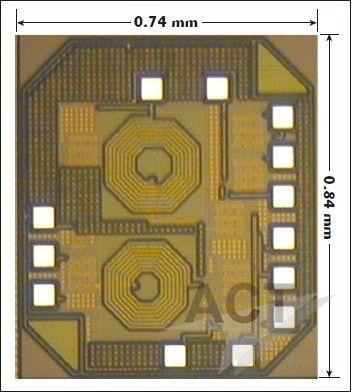

LNA的芯片显微照片如图5所示。

总面积包括输出缓冲区和0.74×0.84 mm的焊盘(pad)。

图6显 示了提出的LNA的电压增益、S11和S22。

还制作了一个与提出的LNA相同功耗水平和输出负载条件的L-CSLNA。

在2.4 GHz时LNA的电压增益为21.5 dB,而L-CSLNA的电压增益为18.8 dB。

测得的LNA的增益是2.7 dB,高于L-CSLNA。

提出的LNA具有良好的输入和输出匹配。

在2.4 GHz条件下,S11的值是12 dB,S22的值是-16 dB。

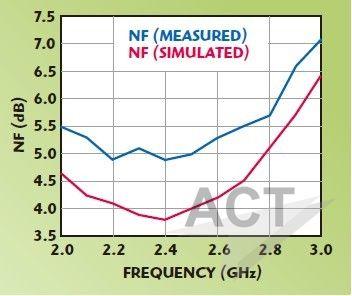

如图7所示,相应的NF为4.9 dB。

实测的NF超过了仿真的NF,达1 dB。

这个大的差异归因于恶劣的噪声建模和工艺变化。

IEEE.802.15.4接收器可以容许LNA和混频器的噪声系数为11.2或10.5 dB1。

如果我们的LNA用在接收器前端,就需要一个NF小于19.8 dB的混频器。

这样一个宽松的NF要求用目前的CMOS混频器设计不难实现。

LNA的IIP3为-12 dBm。

核心LNA从1 V电源电压汲取(draw)0.6 mA。

总功耗仅为0.6 mW。

这个LNA与文献中公布结果的比较列于表1。

虽然几个LNA11-14 都有较好的NF,但比提出的LNA消耗的功率更多。

此外,这种低NF对应用是没有必要的1,与提出的LNA相比性能相当类似。

不过,该LNA采用了一个大电阻负载来实现高增益。

因此,它不能在1 V的低电源电压下操作。

部分LNA13,14 显示了增益和线性度之间的折衷。

它们的IIP3较高,但功耗要高得多,增益比提出的LNA低得多。

根据表1计算的FOM,该LNA具有最好的FOM1和可接受FOM2。

结论

本文提出了一个新的输入匹配拓扑结构,无需对CSLNA增益进行折衷。

输入网络使用电容反馈和网络实现。

基于这种方法,CSLNA能够实现更高的增益,同时保持良好的输入匹配和低功耗。

本文解释了LNA的设计和制作的设计方法。

与L-CSLNA相比,淘汰了源电感Ls,并获得了较高的增益。

提出的LNA仅消耗0.6 mW,同时提供了非常高的增益、良好的输入匹配和适中的NF。

大电流电感基于DSP 56F801的正弦波输出DC/AC电源设计方案

目前,小功率DC/AC电源在UPS以及可再生能源领域(如光伏户用电源)得到了广泛的应用。该类电源的功能是将低压直流转换为市电交流。这类电源的一种主电路结构是由高频DC/D

M级电感问题怎么测准备入手EG8010,想用EE85做个3000W的电源但发现后电感是3MH的手上没有,请问这个电感怎么绕磁芯磁环的手上到是有些,另外我只有示波器和万用表怎么测电感值,(示波器上有个0.5Vpp 1

简单的电感/电容表制作 一、原理图

电子爱好者在制作均衡电容、音箱分频电感时,稍有误差就会令音质受到损害。这里向广大爱好者介绍一款制作简单的电感/电容表,电路数字

在线客服1

在线客服1